# **EVERLIGHT** AMERICAS

# DATASHEET

# Proximity Sensor with I<sup>2</sup>C Interface EAAPMST3923A1

# Feature

- PS

- -low power consumption

- -narrow band IR spectrum

- -programmable IRED intensity

- -programmable periodic sleep time between each measurement

- Interrupts

adjustable interrupt persistency

- Green Power

-less than 10µA DC supply current during sleep time

-less than 0.1µA supply current when powered down

- Easy to Use

SMBus Compatible I<sup>2</sup>C interface

-auto register addressing

-temperature compensation

-interrupt pin and flags

- Wide Operating Voltage Range

-1.7V to 3.6V supply for I<sup>2</sup>C interface

-2.3V to 3.6V sensor power supply

-I<sup>2</sup>C address selection (bonding optional)

- Wide Operating temperature Range -40°C to 85°C ambient temperature

- Size

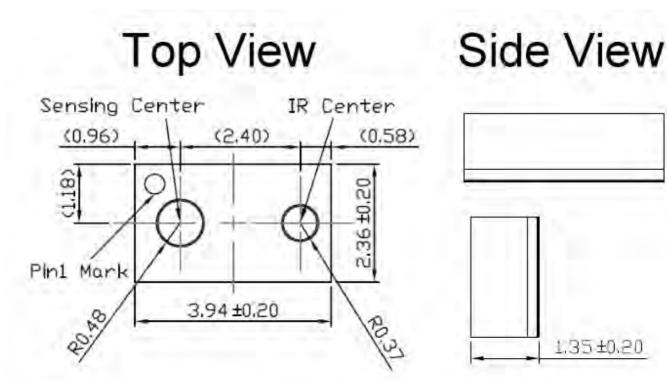

-3.94mm (L) x2.36mm (W) x1.35mm (H)

- The product itself will remain within RoHS compliant version

- Compliance with EU REACH

- Compliance Halogen Free(Br < 900ppm, Cl < 900ppm, Br+Cl < 1500ppm)

# General Description

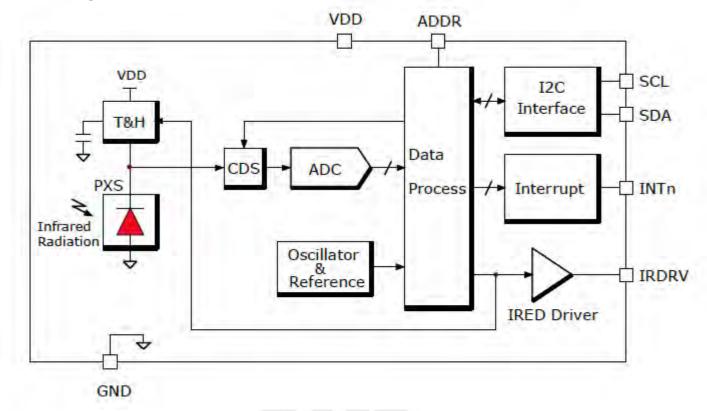

The EAAPMST3923A1 integrates a proximity sensor (PS), an infrared emitting diode (IRED) driver and an SMBus compatible I<sup>2</sup>C interface into one chip. The fast I<sup>2</sup>C interface (up to 750 kHz) is for easy connection to a micro-controller or embedded controller. A flexible interrupt scheme is provided for minimal micro-controller utilization. The EAAPMST3923A1 is featuring low power operation, most suitable for battery powered apparatus.

The proximity sensor (PS) employs a narrow-band, multi-layer optical coating to suppress most infrared background. Synchronized with the built-in IRED driver, the proximity sensing circuitry adopts track-and-hold (T&H) and correlated double sampling (CDS) techniques to reject non-synchronized infrared signals and electrical DC offset. Each proximity measurement takes about 0.8mS, and various sleep-time in between can be programmed through I<sup>2</sup>C interface to reduce overall power consumption.

The EAAPMST3923A1 provides a separate pin for level-style interrupt which simplifies and improves system efficiency by eliminating the need to poll a sensor for PS readings. An interrupt is generated when the PS reading exceeds the upper threshold. In addition, a programmable interrupt persistence feature allows the user to determine how many consecutive exceeded readings are necessary to trigger an interrupt. Interrupt threshold and persistence settings are configurable through I<sup>2</sup>C interface.

# Applications

- Display and keypad dimming adjustment and proximity sensing for:

-Mobile Devices: smart phone, PDA, GPS

-Computing Devices: laptop PC, notebook

- -Consumer Devices: LCD-TV, digital picture frame, digital camera

EVERLIGHT AMERICAS

Package Dimensions

# **Bottom View**

Unit: mm Tolerances: ± 0.2mm

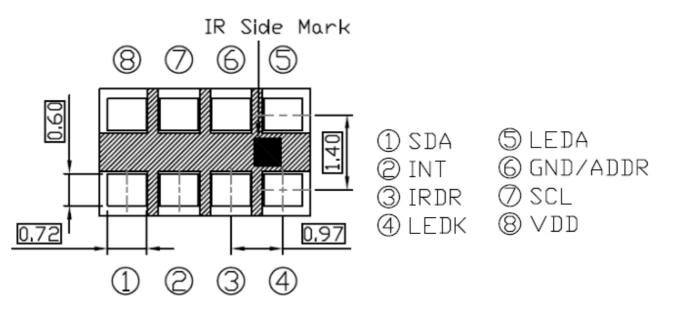

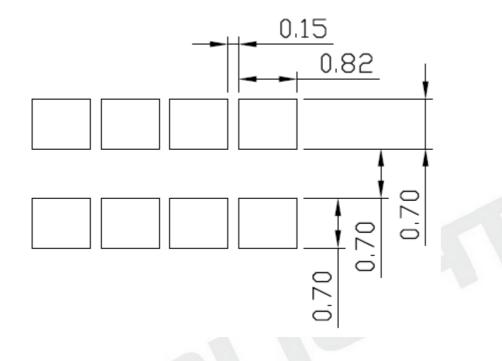

# PCB Layout Footprint

# **Pin Description**

| Pin No. | Pin name                                                            | Pin function                                                       |  |

|---------|---------------------------------------------------------------------|--------------------------------------------------------------------|--|

| 1       | SDA                                                                 | I2C serial data line                                               |  |

| 2       | INT Interrupt pin: LO for interrupt alarming. The INT pin is an ope |                                                                    |  |

| 3       | IRDR                                                                | IR LED driver pin connecting to the cathode of the external IR LED |  |

| 4       | LEDK                                                                | Cathode of the embedded IR LED, connect to IRDR pin                |  |

| 5       | 5 LEDA Anode of the embedded IR LED, connect to power               |                                                                    |  |

| 6       | GND                                                                 | Ground: The thermal pad is also connected to the GND pin           |  |

| 7       | 7 SCL I2C serial clock line                                         |                                                                    |  |

| 8       | VDD                                                                 | Power supply voltage: 2.3V ~ 3.6V                                  |  |

# **Block Diagram**

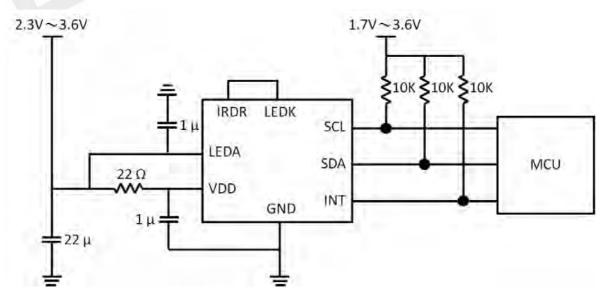

# Typical Application Circuit

A typical application for the EAAPMST3923A1 is shown in Figure 1. The EAAPMST3923A1's  $I^2C$  address is 0x45 when ADDR is tied to GND. The device can be tied onto a system's  $I^2C$  bus together with other  $I^2C$  compliant devices.

# Layout Considerations

The EAAPMST3923A1 is relatively insensitive to layout. Like other I<sup>2</sup>C devices, it is intended to provide excellent performance even in significantly noisy environments. There are only a few considerations that will ensure best performance. Route the supply and I<sup>2</sup>C traces as far as possible from all sources of noise. A  $0.1\mu$ F and  $1\mu$ F power supply decoupling capacitors need to be placed close to the device.

# Absolute Maximum Ratings ( $T_A = +25^{\circ}C$ )

| Parameter                               | Rating                                                                                                                              | Unit                 |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| VDD supply voltage                      | 4.0                                                                                                                                 | V                    |

| I <sup>2</sup> C bus voltage (SCL, SDA) | -0.5 to 4.0                                                                                                                         | V                    |

| I <sup>2</sup> C bus current (SCL, SDA) | < 10                                                                                                                                | mA                   |

| IRDRV pin voltage                       | 5.5                                                                                                                                 | V                    |

| ADDR pin voltage                        | -0.5 to VDD+0.5                                                                                                                     | V                    |

| INTn pin voltage                        | -0.5 to 4.0                                                                                                                         | V                    |

| INTn pin current                        | < 10                                                                                                                                | mA                   |

| ESD Rating (HBM)                        | 8                                                                                                                                   | KV                   |

| -                                       | the maximum ratings listed for extended periods of time. Exposure<br>ct reliability and result in failures not covered by warranty. | e to such conditions |

Important Note: All parameters having Min/Max specifications are guaranteed. Typical values are information purposes only. Unless otherwise noted, all tests are the specified temperature and pulsed tests, therefore:  $T_J=T_C=T_A$

# Electrical Characteristics (VDD=3.0V, T<sub>A</sub>=+ $25^{\circ}C$ )

| Parameter              | Descriptions                                              | Conditions                                        | Min. | Тур. | Max. | Unit   |

|------------------------|-----------------------------------------------------------|---------------------------------------------------|------|------|------|--------|

| V <sub>DD</sub>        | Power supply range                                        |                                                   | 2.3  | 3.0  | 3.6  | V      |

| I <sub>DD_OFF</sub>    | Supply current when PS is disabled                        | PS_EN = 0                                         | -    | 0.01 | 0.1  | μA     |

| IDD(PEAK)              | Peak supply current while<br>measurement is talking place | PS_EN = 1<br>(not including IRED driving current) | -    | 85   |      | μA     |

| I <sub>DD(SLEEP)</sub> | Supply current during sleep time                          | PS_EN = 1<br>(not including IRED driving current) | -    | 10   | -    | μA     |

| Count <sub>PS_DK</sub> | PS measurement w/o object in path                         |                                                   | -    | 0    | 10   | counts |

| Count <sub>PS_FS</sub> | Full scale of PS output                                   |                                                   | -    | -    | 255  | counts |

| Count <sub>PS_1</sub>  | PS measurement IR_PULSE=0                                 | 850nm IRED, fixed distance                        | 20   | 25   | 30   | counts |

| Count <sub>PS_2</sub>  | PS measurement IR_PULSE=1                                 | 850nm IRED, fixed distance                        | 40   | 50   | 60   | counts |

| Count <sub>PS_3</sub>  | PS measurement IR_PULSE=2                                 | 850nm IRED, fixed distance                        | 80   | 100  | 120  | counts |

| Count <sub>PS_4</sub>  | PS measurement IR_PULSE=3                                 | 850nm IRED, fixed distance                        | 160  | 200  | 240  | counts |

| tr                     | Rise time for IRDR sink current                           | R <sub>LOAD</sub> = 15Ω at IRDR, 20% to 80%       | -    | 0.5  | -    | μS     |

| t <sub>f</sub>         | Full time for IRDR sink current                           | $R_{LOAD}$ = 15 $\Omega$ at IRDR, 80% to 20%      | -    | 0.5  | -    | μS     |

| IRDRV_0                | IRDRV driving current (sink)                              | VIRDRV =0.5V                                      | 85   | 100  | 115  | mA     |

| IRDRV_LEAK             | IRDRV leakage current                                     | PS_EN = 0, VDD = 3.6V                             |      | 0.01 | 0.1  | μA     |

| VIRDRV                 | Sustained voltage on IRDRV                                |                                                   | -    | -    | 3.6  | V      |

| f <sub>I2C</sub>       | I <sup>2</sup> C clock rate                               |                                                   | 0    | -    | 750  | KHz    |

| VI2C                   | Supply voltage range for I <sup>2</sup> C interface       |                                                   | 1.7  | -    | 3.6  | V      |

| VIL                    | SCL and SDA input low voltage                             |                                                   | -    | -    | 0.55 | V      |

| VIH                    | SCL and SDA input high voltage                            |                                                   | 1.25 | -    | -    | V      |

| ISDA                   | SDA current sinking capability                            | V <sub>OL</sub> = 0.4V                            | 2.7  | 5    | -    | mA     |

| I <sub>INTn</sub>      | INTn current sinking capability                           | V <sub>OL</sub> = 0.4V                            | 2.7  | 5    | -    | mA     |

| SR_VDD                 | Power-up slew rate                                        | VDD rising edge between 0.4V and 2.3V             | 0.5  | -    | -    | V/ms   |

| Parameter               | Descriptions                                                      | Conditions                                           | Min.                | Тур. | Max. | Unit |

|-------------------------|-------------------------------------------------------------------|------------------------------------------------------|---------------------|------|------|------|

| VI <sup>2</sup> C       | Supply voltage range for I <sup>2</sup> C interface               |                                                      | 1.7                 | -    | 3.6  | V    |

| <b>f</b> <sub>SCL</sub> | SCL clock frequency                                               |                                                      | -                   | -    | 750  | KHz  |

| VIL                     | Low level input voltage of SCL and SDA                            |                                                      | -                   | -    | 0.55 | V    |

| VIH                     | High level input voltage of SCL and SDA                           |                                                      | 1.25                | -    | -    | V    |

| V <sub>hys</sub>        | Hysteresis of Schmitt trigger input                               |                                                      | 0.05V <sub>DD</sub> | -    | -    | V    |

| Vol                     | Low-level output voltage (open-drain) at 4mA sink current         |                                                      | -                   | -    | 0.4  | V    |

| li                      | Input leakage for each SDA, SCL                                   |                                                      | -10                 | -    | 10   | μA   |

| tsp                     | Pulse width of spikes that must be suppressed by the input filter |                                                      | -                   | -    | 50   | nS   |

| taa                     | SCL falling edge to SDA output data valid                         |                                                      | -                   | -    | 0.9  | μS   |

| Ci                      | Capacitance for each SDA and SCL pin                              |                                                      |                     | -    | 10   | pF   |

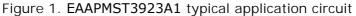

| thd:sta                 | Hold time (repeated) START condition                              |                                                      | 0.6                 | -    | -    | μS   |

| t <sub>LOW</sub>        | Low period of the SCL clock                                       |                                                      | 1.3                 | -    |      | μS   |

| tнigн                   | High period of the SCL clock                                      |                                                      | 0.6                 | -    | -    | μS   |

| tsu:sta                 | Set-up time for a repeated START condition                        |                                                      | 0.6                 | -    | -    | μS   |

| thd:dat                 | Data hold time                                                    |                                                      | 30                  | -    | -    | nS   |

| tsu:dat                 | Data set-up time                                                  |                                                      | 100                 | -    | -    | nS   |

| tsu:sto                 | Set-up time for STOP condition                                    |                                                      | 0.6                 | -    | -    | μS   |

| tBUF                    | Bus free time between a STOP and START condition                  |                                                      | 1.3                 | -    | -    | nS   |

| Tr                      | Rise time of both SDA and SCL                                     | $R_{pull-up} = 10K\Omega, C_b = 10pF$                | -                   | 95   |      | nS   |

| T <sub>f</sub>          | Fall time of both SDA and SCL                                     | $R_{pull-up} = 10K\Omega, C_b = 10pF$                |                     | 25   |      | nS   |

| Cb                      | Capacitive load for each bus line                                 |                                                      | -                   | -    | 0.4  | nF   |

| R <sub>pull-up</sub>    | SDA and SCL system bus pull-up resistor                           | Maximum is determined by $t_{\rm R}$ and $t_{\rm f}$ | -                   | 10   | -    | ΚΩ   |

| t <sub>vd:dat</sub>     | Data valid time                                                   |                                                      | -                   | -    | 0.9  | μS   |

| tvd:ack                 | Data valid to acknowledge time                                    |                                                      | -                   | -    | 0.9  | μS   |

| VnL                     | Noise margin at the LOW level                                     |                                                      | 0.1V <sub>DD</sub>  | -    | -    | V    |

| $V_{nH}$                | Noise margin at the HIGH level                                    |                                                      | $0.2V_{\text{DD}}$  | -    | -    | V    |

# $I^{2}C$ Electrical Specifications (VDD=3.0V, T<sub>A</sub>=+25°C)

Note: The I<sup>2</sup>C bus protocol was developed by Philips (now NXP). For a complete description of the I<sup>2</sup>C protocol, please review the NXP I<sup>2</sup>C design specification at <u>http://www.i2c-bus.org/references/</u>.

# I<sup>2</sup>C Timing Diagram

Figure 2. I<sup>2</sup>C Timing Diagram

# **Register Map**

There are six 8-bit registers accessible via I<sup>2</sup>C. Registers 0x01 and 0x02 define the operation mode of the device. Register 0x03 and 0x04 store the PS thresholds which trigger interrupt events. Register 0x05 store the PS readings.

| REG  | REG        |                 | BIT                                         |   |       |          |      | Default |   |         |

|------|------------|-----------------|---------------------------------------------|---|-------|----------|------|---------|---|---------|

| ADDR | NAME       | 7               | 6                                           | 5 | 4     | 3        | 2    | 1       | 0 | Default |

| 0x00 | Product ID |                 | Product ID Code for Communication Link Test |   |       |          |      | 0x24    |   |         |

| 0x01 | CONFIGURE  | PS_EN           | N SLEEP_TIME IR_PULSE PERST                 |   |       |          | 0x00 |         |   |         |

| 0x02 | INTERRUPT  | PS_FLAG Write 0 |                                             |   |       |          | 0x00 |         |   |         |

| 0x03 | PS_LT      |                 | PS_LT[7:0]                                  |   |       |          |      | 0x00    |   |         |

| 0x04 | PS_HT      |                 | PS_HT[7:0]                                  |   |       |          |      | 0xFF    |   |         |

| 0x05 | PS_Reading |                 |                                             |   | PS_DA | ATA[7:0] |      |         |   | 0x00    |

# Register 0x01 (Configure)

| Regis | ter 0x0 | 91 (Con | figure)                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------|---------|---------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit # | Access  | Default | Name                     | Function / Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 7     | RW      | 0x00    | PS_EN<br>(PS Enable)     | When = 0, proximity sensing is disabled.<br>When = 1, proximity sensing is enable.<br>Proximity reading will be ready 2ms after this bit is set high                                                                                                                                                                                                                                                                                                                                 |

| 6:4   | RW      | 0x00    | SLEEP_TIME<br>(PS Sleep) | For bits 6:4 = (see the following)<br>111; sleep time between PS IR LED pulse is 0.0ms (run continuously)<br>110; sleep time between PS IR LED pulse is 12.5ms<br>101; sleep time between PS IR LED pulse is 50ms<br>100; sleep time between PS IR LED pulse is 75ms<br>011; sleep time between PS IR LED pulse is 100ms<br>010; sleep time between PS IR LED pulse is 200ms<br>001; sleep time between PS IR LED pulse is 400ms<br>000; sleep time between PS IR LED pulse is 800ms |

| 3:2   | RW      | 0x00    | IR_PULSE                 | For bits 3:2 = (see the following)<br>00: one unit<br>01: two units<br>10: four units<br>11: eight units                                                                                                                                                                                                                                                                                                                                                                             |

| 1:0   | RW      | 0x00    | PERST                    | For bits 1:0 = (see the following)<br>00: set INT_FLAG if 1 reading trips the threshold<br>01: set INT_FLAG if 4 reading trips the threshold<br>10: set INT_FLAG if 8 reading trips the threshold<br>11: set INT_FLAG if 16 reading trips the threshold                                                                                                                                                                                                                              |

# Register 0x02 (Interrupt)

| Bit # | Access | Default | Name      | Function / Operation                                             |

|-------|--------|---------|-----------|------------------------------------------------------------------|

| 7     | RW     | 0x00    | INT_FLAG  | When = 1, PS interrupt event occurred. Reset when PS reading is  |

| '     |        | 0,00    | (PS Flag) | below the low threshold or by a write-operation on Register 0x02 |

# Register 0x03 (PS\_LT)

| Bit # | Access | Default | Name                    | Function / Operation          |

|-------|--------|---------|-------------------------|-------------------------------|

| 7:0   | RW     | 0x00    | PS_LT<br>(PS Threshold) | 8-bit low interrupt threshold |

# Register 0x04 (PS\_HT)

| Bit # | Access | Default | Name           | Function / Operation           |

|-------|--------|---------|----------------|--------------------------------|

| 7:0   | RW     | 0xFF    | PS_HT          | 8 bit high interrupt threshold |

| 7.0   | L M    | UXFF    | (PS Threshold) | 8-bit high interrupt threshold |

# Register 0x08 (PS\_DATA)

| Bit | Access | Default | Name                        | Function / Operation |

|-----|--------|---------|-----------------------------|----------------------|

| 7:0 | RO     | 0x00    | PS_DATA<br>(Proximity Data) | 8-bit PS reading     |

### 1. Principles of Operation

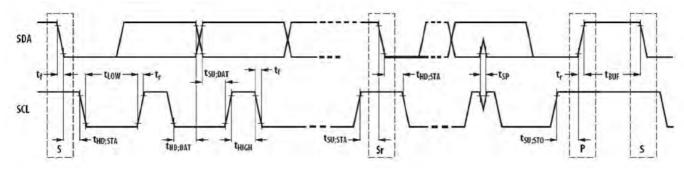

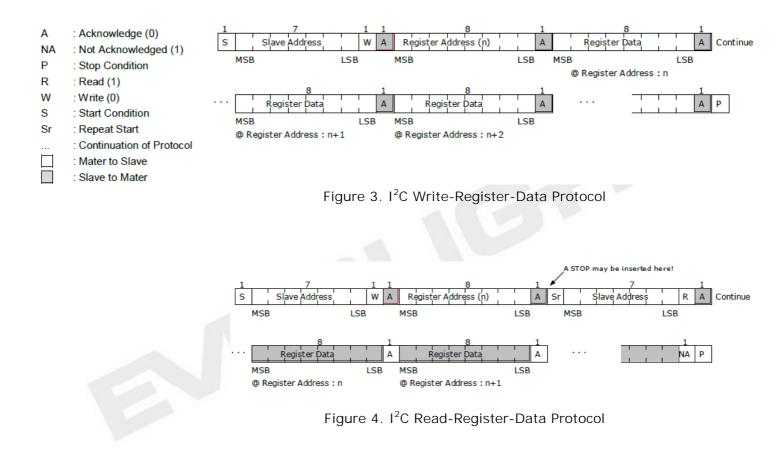

# I<sup>2</sup>C Read/Write Register Data

The EAAPMST3923A1's I<sup>2</sup>C slave address is 0x45 when ADDR pad is tied to GND. Below picture detail the protocol of writing or reading the register data inside the EAAPMST3923A1.

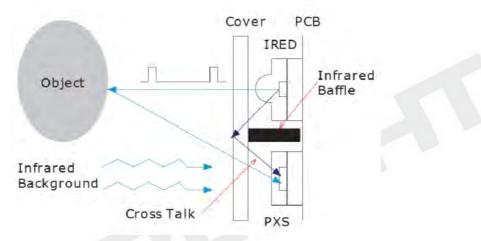

#### Proximity Sensing

As illustrated in below picture, an infrared emitter (IRED), driven by the PS circuitry, emits synchronized infrared pulsed. The object on the light path reflects the infrared radiation pulsed that are detected by the PS. With a narrow band optical coating on the proximity sensor, the PS only receives the infrared around 850nm wavelength, rejecting most ambient light interference. By using the track-and hold (T&H) and correlated double sample (CDS) techniques, the PS is capable of measuring the intensity of reflected infrared pulsed. Proper infrared baffle may be required due to the crosstalk from IRED to PS.

Figure 5. Proximity Sensing

When the EAAPMST3923A1's proximity sensing is enable (PS\_EN=1), the PS takes the time of (PULSE\_NUM+1) x 0.5mS to take one measurement. The pulsed driving current of the IRED is 100mA in amplitude. The sleep time ( $t_{sleep}$ ) between proximity measurements is determined by setting the PS\_SLP. bits.

100mA x 50uS /( tsleep + 0.4mS) , when PULSE\_NUM=0 ; 100mA x 100uS /( tsleep + 0.4mS) , when PULSE\_NUM=1 ; 100mA x 200uS /( tsleep + 0.8mS) , when PULSE\_NUM=2 ; and 100mA x 400uS /( tsleep + 1.6mS) , when PULSE\_NUM=3 .

#### Interrupt Function

Interrupt INT\_FLAG is set when the PS reading is more than the high threshold (PS\_HT). INT\_FLGA is cleared when the PS reading (PS\_DAT) is lower than the low threshold (PS\_LT), or when a write-operation is done on Register 0x02. To further control when an interrupt occurs, EAAPMST3923A1 provides a persistence filter which allows the user to specify the number of consecutive occurrences of proximity readings tripping over the threshold before an interrupt is generated.

The configuration register (Register 0x01) allows the user to set the proximity persistence (PRST) values. See the configuration register for details on the persistence filter values.

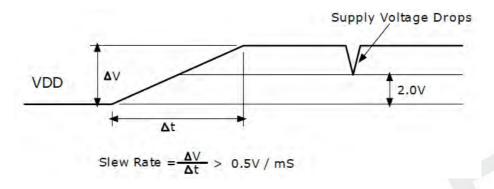

#### VDD Power-up and Power Supply

Upon power-up, please ensure the slew rate of VDD greater than 0.5V/mS. After power-up, the supply voltage shall NOT drop below 2.0V. Once it happens, please switch off the power, wait more than 1 second, and then power on the device again.

Figure 6. Waveform of Supply Voltage VDD

#### Power-Down

To put the EAAPMST3923A1 into a power-down state, the user can set both PXS\_EN to 0; or more simply, reset Register 0x01.

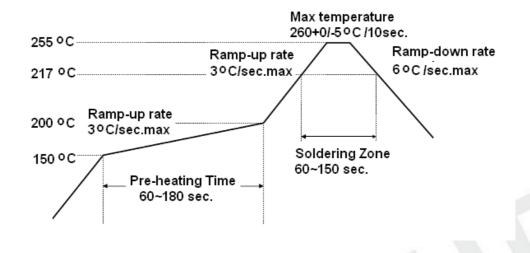

# **Recommended Solder Profile**

#### Notice:

- 1. Reflow soldering should not be done more than two times.

- 2. When soldering, do not put stress on the devices during heating.

- 3. After soldering, do not warp the circuit board.

# Soldering Iron

Each terminal is to go to the tip of soldering iron temperature less than  $350^{\circ}$ C for 3 seconds within once in less than the soldering iron capacity 25W. Leave two seconds and more intervals, and do soldering of each terminal. Be careful because the damage of the product is often started at the time of the hand solder.

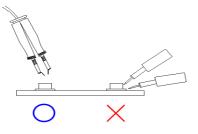

# Repairing

Repair should not be done after the device have been soldered. When repairing is unavoidable, a double-head soldering iron should be used (as below figure). It should be confirmed beforehand whether the characteristics of the device will or will not be damaged by repairing.

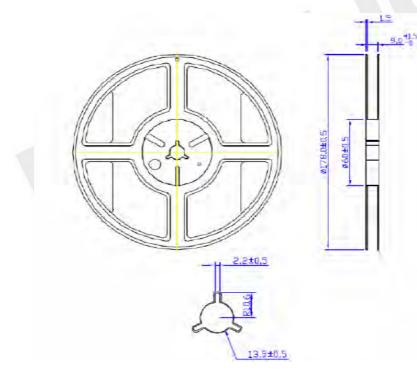

# Packing Quantity Specification

2000 PCS/ 1 Reel

# Label Format

**Reel Dimensions**

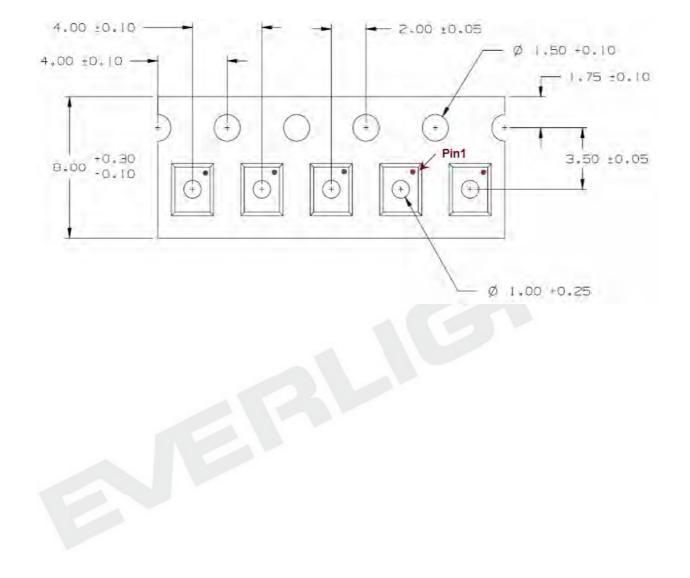

# **Tape Dimensions**

#### DISCLAIMER

- 1. EVERLIGHT reserves the right(s) on the adjustment of product material mix for the specification.

- 2. The product meets EVERLIGHT published specification for a period of twelve (12) months from date of shipment.

- 3. The graphs shown in this datasheet are representing typical data only and do not show guaranteed values.

- 4. When using this product, please observe the absolute maximum ratings and the instructions for using outlined in these specification sheets. EVERLIGHT assumes no responsibility for any damage resulting from the use of the product which does not comply with the absolute maximum ratings and the instructions included in these specification sheets.

- 5. These specification sheets include materials protected under copyright of EVERLIGHT. Reproduction in any form is prohibited without obtaining EVERLIGHT's prior consent.

- 6. This product is not intended to be used for military, aircraft, automotive, medical, life sustaining or life saving applications or any other application which can result in human injury or death. Please contact authorized Everlight sales agent for special application request.